Webinars and Datatips from the experts

OrCAD Library and Database Overview

Here we explore some of the different options available for OrCAD libraries and databases. This webinar is about 30 minutes.

OrCAD PCB Professional Overview

Here we explore the OrCAD PCB Professional Suite. This webinar is about 30 minutes long

Allegro PCB High Speed Option Webinar

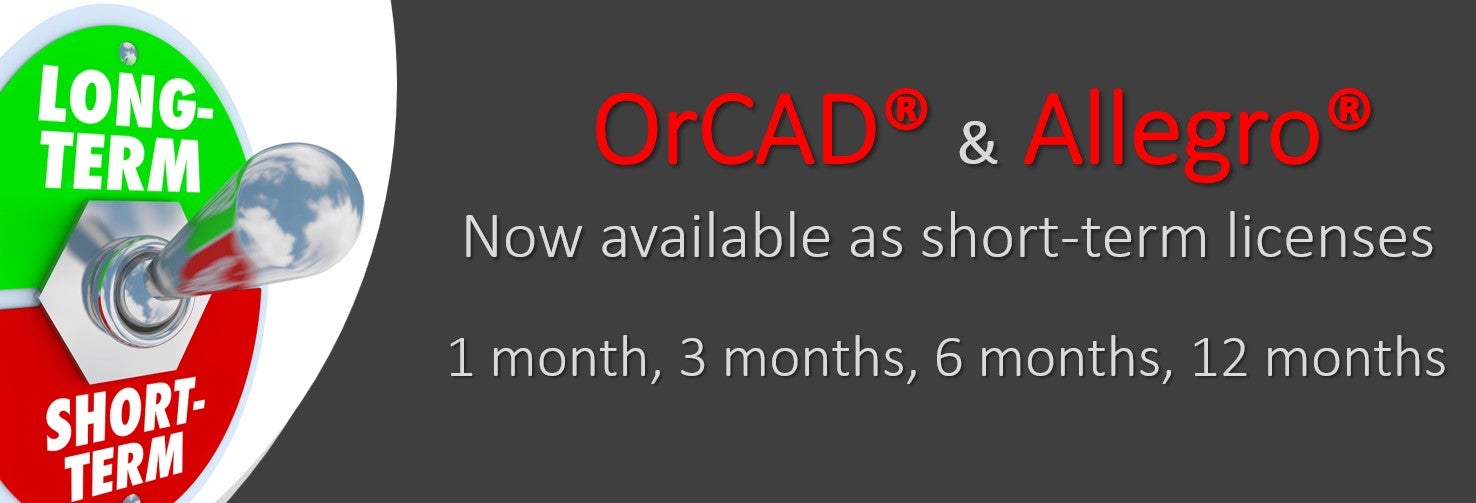

Here we explore a 20 minute overview of the Cadence Allegro PCB High Speed Option. Available to rent for periods as short as one month

Team-Source Your PCB Layout with Allegro PCB Symphony Team DesignShow, share, and collaborate on your most complex PCB designs in real-time, without setting up a dedicated server. Allegro® PCB Symphony Team Design Option is the easiest way to collaborate on PCB design.

|

Allegro ECAD-MCAD Library CreatorThe Cadence Allegro ECAD-MCAD Library Creator allows you to create new standards-compliant libraries in a fraction of the time, synchronize your ECAD and MCAD libraries, and easily retarget your existing l...

|

Accelerating DO-254 Approval with Cadence ToolsThis white paper explores software tools as they relate to meeting the DO-254 Design Assurance Guidance for Airborne Electronic Hardware specifications, and what steps must be performed in order to use you...

431 KB

|

LG Soft India Uses Tempus PBA for Slack-Based Optimization FlowHear how the LG Soft Mobile processor backend team moved to a more realistic timing signoff environment. Using the Cadence(r) Tempus(tm) PBA Signoff Solution and Innovus(tm)

|

PhoeniX Software: Developing First-Time-Right Photonic ICsTwan Korthorst, CEO of PhoeniX Software, discusses integrated design development for photonic ICs and how to leverage the Cadence® Virtuoso® design flow with PhoeniX Software’s dedicated photonic layout

|

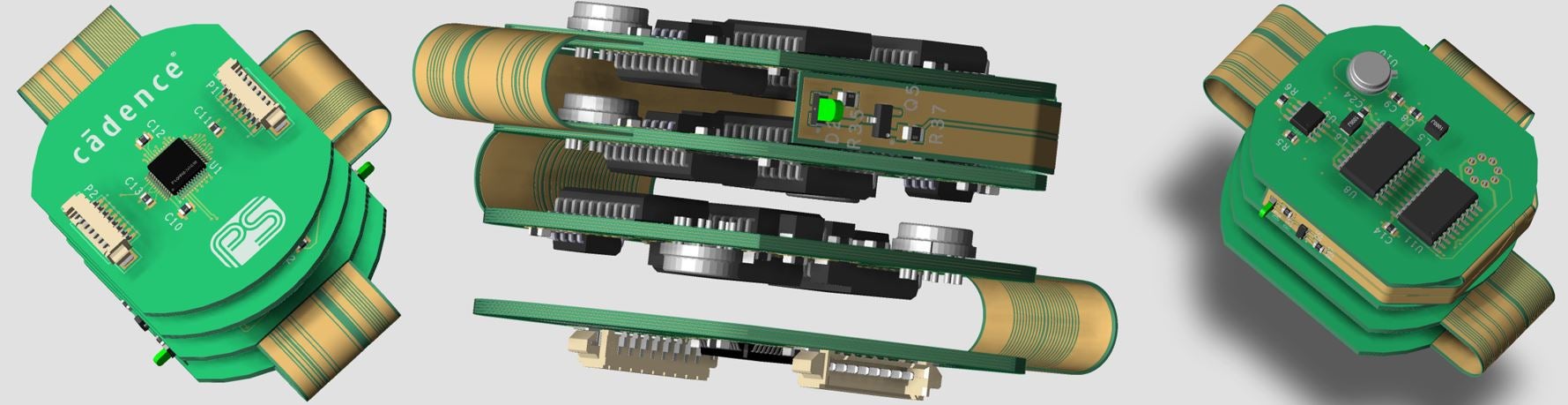

Avoid Costly Fabrication Errors with Real-Time Inter-Layer ChecksRigid-flex technology lets us create smaller PCBs than ever before. And these PCBs are making our lives better in the form of wearable, mobile, and medical devices. That’s exactly why failure is not an option

|

Cadence Senior Vice President and Chief Financial Officer Geoff Ribar to Present at Barclays Global Technology, Media and Telecommunications ConferenceGeoff Ribar, Cadence Design Systems, Inc. (NASDAQ: CDNS) SVP & CFO, will speak at Barclays Global Technology, Media and Telecommunications Conference

|

Learning Map for All BUsCadence training learning maps

617 KB

|

Bluetooth 5: Making Mobile Connectivity Seamless in an IoT WorldTired of struggling with pairing your Bluetooth devices and getting them to work with each other? In this week’s Whiteboard Wednesdays video, Scott Jacobson explains how Bluetooth 5 does away with this

|

Sigrity Tech Tip: How to Accelerate Accurate 3D Full Wave Extraction TimeAllegro Sigrity SI Base (http://goo.gl/L1k5GX) and the System Serial Link Analysis Option (http://goo.gl/L03MLd) from Cadence are demonstrated. Sigrity technologist Brad Brim guides you step by step

|

Multi-Board Electrical and Thermal Co-simulation using PowerDC |

DesignCon 2015: Sigrity 2015 Portfolio HighlightsBrad Brim, Cadence product engineering architect, discusses the company’s DesignCon 2015 highlights ranging from power-aware design for parallel buses and serial interconnect design to the Sigrity

|

Sigrity Tech Tip: How PCB Designers Can Find and Fix Power Integrity ProblemsLearn about Allegro Sigrity PI Base (http://goo.gl/k7XCaG) through a demonstration. Sigrity technologists will show how PCB Designers are empowered to solve basic PI problems early in the design cycle

|

Sigrity Tech Tip: How DDR interfaces can be accurately analyzed pain-free (without large S-parameters)Allegro Sigrity SI Base (http://goo.gl/L1k5GX) and Power-Aware SI Option (http://goo.gl/8uouKV) from Cadence are demonstrated. Sigrity technologists guide you step by step on how to use the Sigrity tools

|

Sigrity Tech Tip: How to Build an IBIS-AMI ModelCadence Sigrity technologists guide you step by step on how to build an IBIS-AMI model without having to write any code using Allegro Sigrity SI Base and the System Serial Link Analysis Option.

|

Gain an Unfair Advantage - Make Better Products Faster with Cadence PCB ToolsThey’re coming for you, and they’re coming with everything they’ve got. Your competition has set their sights on your company, your product, you. What can you do, as the PCB designer, to make better products

|

Cadence Senior Vice President and Chief Financial Officer Geoff Ribar to Present at the NASDAQ 35th Investor ProgramGeoff Ribar, Cadence Design Systems, Inc. (NASDAQ: CDNS) SVP & CFO, will speak at the NASDAQ 35th Investor Program in London at the Mayfair hotel …

22 Nov 2016

|

Cadence President and CEO Lip-Bu Tan to Present at Credit Suisse Technology, Media, & Telecom ConferenceLip-Bu Tan, Cadence Design Systems, Inc. (NASDAQ: CDNS) President & CEO, will speak at Credit Suisse Technology, Media, & Telecom Conference in Scottsdale, AZ at The Phoenician …

22 Nov 2016

|

Cadence and Silicon Laboratories Success StorySilicon Labs used the wreal construct along with RVMs to accurately and easily create its mixed-signal environment.

619 KB

|

Analog Behavioral Modeling and Model Generation17 Nov 2016

|

Ericsson Meets DDR and PCIe Specs While Avoiding CrosstalkIn this Expert Insights video from CDNLive India 2014, Sheetal Jain, a member of the modem organization at Ericsson Design, discusses how his team verified their design to meet DDR and PCIe specs while avo...

16 Nov 2016

|

Sigrity Tech Tip: How to Build Accurate Leadframe Package Models Quickly and EasilyAllegro Sigrity SI Base (http://goo.gl/L1k5GX) and the Package Assessment and Extraction Option (https://goo.gl/2cYFsA) from Cadence are demonstrated. Sigrity technologists guide you step by step on how ...

16 Nov 2016

|

Sigrity Tech Tip: How PCB Designers Can Jump Start Electrical Sign off Using Power-Aware Rule ChecksSigrity technologists guide you step by step on how to utilize power-aware electric rule checks to confidently fast track the sign off process for your PCB designs. Includes demonstrations of Allegro Sigri...

16 Nov 2016

|

Sigrity Tech Tip How to Accurately Model a Multi-Gigabit Serial Link 10 Times FasterLearn about Allegro Sigrity SI Base (http://goo.gl/L1k5GX) and the System Serial Link Analysis Option (http://goo.gl/L03MLd) through a demonstration. Sigrity technologists guide you step by step on how to ...

16 Nov 2016

|

Sigrity Tech Tip: How to Find Signal Integrity Problems on an Unrouted PCBLearn about Allegro Sigrity SI Base (http://goo.gl/L1k5GX) and the new flow planning feature for route planning with signal integrity analysis through a brief demonstration. Sigrity technologists guide you...

16 Nov 2016

|

System Signal Integrity Expands into the Lab16 Nov 2016

|

MIPI Alliance InterfacesIn this week's Whiteboard Wednesdays video, Moshik Rubin takes a closer look at the popularity of CSI2, DSI and other common MIPI protocols.

15 Nov 2016

|

Software-Driven Verification IP (VIP)In this week's Whiteboard Wednesdays video, we discuss about integration of IP in a SoC context. Patrick Oury explains how to use Cadence Verification IP (VIP) to coordinate SoC activation together with fu...

15 Nov 2016

|

Optimized FFTs on the Tensilica ConnX BBE32EP DSPFast Fourier transform (FFT) is a key kernel in almost all DSP applications, and an important benchmark for assessing the efficiency of a DSP. In this week's Whiteboard Wednesdays video, Pushkar Patwardha...

15 Nov 2016

|

Industry Trends and Requirements for Autonomous DrivingIn this week's Whiteboard Wednesdays video, the first in a three part series focusing on Functional Safety for autonomous driving, Charles Qi discusses the industry trends and requirements for self-driving...

15 Nov 2016

|

Error Injection: Predefined and CallbacksIn this week's Whiteboard Wednesdays video, James David talks about the benefits of two types of error injection, predefined and callbacks.

15 Nov 2016

|

Cadence Modus Test Solution Enables Support for Safety-Critical SoC Designs Using ARM MBIST InterfaceCadence today announced that the Cadence® Modus™ Test Solution now supports the ARM® Memory Built-In Self Test (MBIST) interface.

14 Nov 2016

|

Silicon Photonics Variation and Design-for-Manufacturability PresentationAs silicon photonics matures into a volume production technology, design-for-manufacturability (DFM) methodologies and techniques are needed in order to ensure both high performance and high yield.

3 MB

|

Heterogeneous Integration on Silicon Electronics and Photonics Design Automation PresentationLearn about recent advances in heterogeneous silicon photonic integration technology and components and the progress in silicon photonic ICs.

10 MB

|

Getting What You’re Entitled to at 10nm by Reducing Timing PessimismThis presentation covers the concept behind SOCV/LVF and the inputs required, and highlights how Cadence® Virtuoso® Variety Statistical Characterization Solution enabled TSMC to meet performance and accura...

11 Nov 2016

|

Rambus Automates ECOs and Saves Time with Cadence Conformal ECO DesignerUsing Cadence ® Conformal ® ECO Designer, Rambus was able to fix logic bugs in one day versus what would have taken one week. The Conformal ECO Designer enabled them to automate and apply more complex fix...

10 Nov 2016

|

GLOBALFOUNDRIES ASIC Design Team Validates Hierarchical Test Architecture using Cadence Test SolutionGLOBALFOUNDRIES needed to create a hierarchical test methodology for highly-complex custom ASICs. The challenge was to be able to seamlessly migrate the architecture without design or compute overhead. Th...

10 Nov 2016

|

Joules RTL Power Solution DatasheetCadence Joules RTL Power Solution closes this gap by delivering time-based RTL power analysis with system-level runtimes and capacity, as well as high-quality estimates of gates and wires based on producti...

66 KB

|

The Formal Verification Book: past and futureGood thing we added cover points … INVERSE (A,B) needed to prove C==0 … But FEV mapping A -> B added too … What did these have in common … FPV: cover points / FEV: tool vacuity ...

1 MB

|

Cadence Releases XJTAG DFT Assistant for OrCAD CaptureCadence today announced that its OrCAD® Capture has been enhanced to now include XJTAG® DFT Assistant, an easy-to-use interface that significantly increases the design for test (DFT) and debug capabilities...

08 Nov 2016

|

GLOBALFOUNDRIES Photonics Summit 2016 Keynote PresentationKeynote: The Time Is Now

15 MB

|

Silicon Photonics PDK Development Presentation15 Gb/s Transmission with Wide-FSR Carrier Injection Ring Modulator for Tb/s Optical Links. An approach to the development of a silicon photonics device library through a CMOS-compatible fabrication facili...

5 MB

|

Working with Photonics Standards PresentationIndustry normative form factors lower the barrier (risk) for adoption of innovative optical technologies. These standards foster innovation yet pose challenges of compliance to electrical interface, softwa...

4 MB

|

Find out the Benefits of Cadence’s Online Training Subscription by Watching this Video.The Online Training Subscription provides an easy and cost effective way to access all the online offerings (online courses, online books, update training) in one or more of the four technology collections...

07 Nov 2016

|

Why You Should Take Genus Synthesis Solution Training Course from CadenceWatch this overview to see why the next-generation Genus Synthesis Solution is gaining popularity, and learn how this Cadence training class can help you optimize the design with massive parallelization, t...

07 Nov 2016

|

Cadence Education Services Training Course on Real Modeling with SystemVerilogAhmed Osman and Moustafa Mohamed from Cadence presented to mixed-signal designers and verification engineers a practical hands-on class on Real-number (RNM) Modeling with SystemVerilog at CDN Live.

04 Nov 2016

|

Why You Should Take Cadence Virtuoso Layout Pro Series T1-T7 Training CourseWatch this overview to understand why Cadence Virtuoso Layout Pro Series T1-T7 is the complete layout automation tool and is so popular with Cadence customers, and learn how this Cadence training class can...

04 Nov 2016

|

Cadence and MathWorks Provide System-Level Simulation Solutions for Mixed-Signal IoT and Automotive ApplicationsCadence today announced it has partnered with MathWorks to streamline system-level design and circuit-level implementation for mixed-signal internet of things (IoT) and automotive applications.

03 Nov 2016

|

Verify Your Design from Concept to Product RealizationThe integration of Cadence PSpice with MathWorks MATLAB and Simulink provides a complete system-level simulation solution for PCB design and implementation. Customers can now utilize PSpice for analog/mixe...

03 Nov 2016

|

Accelerate Your PCB DesignsPCB design is a never-ending cycle—the sooner you can finish one design, the sooner you can get started on the next. Join our webinar and learn how the latest advancements in Cadence® PCB 17.2-2016 technol...

03 Nov 2016

|

Registration for Worldwide MEMS Design Contest OpensCadence, Coventor, X-FAB and Reutlingen University have teamed up to launch the MEMS design contest to encourage the development of innovative MEMS and mixed-signal designs.

02 Nov 2016

|

Why You Should Take the Innovus Implementation System (Block) CourseWatch an overview of the Innovus Implementation System (Block) course to see why this course is so popular with Cadence customers and learn how this class can help you implement your design more efficientl...

31 Oct 2016

|

STMicroelectronics - Improving Productivity with Virtuoso SPDIn this Expert Insights video, Vikas Chelani, Sr. Layout Designer of STMicroelectronics India, describes the challenge of making IP memories compact and efficient despite increased routing and logic comple...

31 Oct 2016

|

Media Alert: Connect, Share and Discuss the Latest Design and Verification Best Practices at Cadence’s Annual Jasper User Group Conference 2016Cadence will host its annual Jasper® User Group (JUG) Conference on November 2 and 3 at the Cadence headquarters in San Jose, Calif.

31 Oct 2016

|

DO-254 Explained White PaperThis white paper explores the high-level concepts and activities within the DO-254 Design Assurance Guidance for Airborne Electronic Hardware specification, why they exist, and what they mean.

221 KB

|

Cadence Senior Vice President and Chief Financial Officer Geoff Ribar to Present at RBC Capital Markets | Technology, Internet, Media and Telecommunications ConferenceGeoff Ribar, Cadence Design Systems SVP & CFO, will speak RBC Capital Markets | Technology, Internet, Media and Telecommunications Conference at The Westin New York at Times …

28 Oct 2016

|

Cadence Senior Vice President and Chief Financial Officer Geoff Ribar to Present at Bernstein Technology Innovation SummitGeoff Ribar, Cadence Design Systems SVP & CFO, will speak at Bernstein Technology Innovation Summit at the New York Hilton Midtown … Webcast available live at cadence.com/company …

28 Oct 2016

|

Great Place to Work and Fortune Name Cadence One of the World’s Best Multinational Workplaces For 2016Cadence today announced it has been named number 15 on the 2016 list of the World’s Best Multinational Workplaces according to global research and consulting firm Great Place to Work® and Fortune magazine....

27 Oct 2016

|

Cadence Delivers Industry’s First Comprehensive TCL1 Documentation to Support Automotive ISO 26262 StandardCadence today announced that it has delivered the industry’s first comprehensive Tool Confidence Level 1 (TCL1) documentation that is compliant with the automotive ISO 26262 standard.

26 Oct 2016

|

Imagine Communications and Cadence Success StoryDesigning Complex, High-Speed Boards with Fewer Re-Spins

|

Omni Design: Increased Speed and Accuracy with Spectre XPSOmni Design Technologies designed their analog and digital circuits simultaneously using Spectre® XPS mixed signal for a faster methodology and a significant improvement in simulation speed without degradi...

25 Oct 2016

|

Cadence Enables Accelerated Implementation and Signoff of New ARM Cortex-M23 and Cortex-M33 ProcessorsCadence today announced the availability of a Rapid Adoption Kit (RAK) for the new ARM® Cortex®-M23 and Cortex-M33 processors targeted for the development of secure Internet of Things (IoT) applications.

25 Oct 2016

|

STREAMLINECADENCE DESIGN SYSTEMS, INC. 24-Oct-16 Page 1 … Third Quarter 2016 Financial Results Conference Call … Remarks of Lip-Bu Tan, President and Chief Executive Officer, and Geoff Ribar …

365 KB

|

CFO Commentary 10.24.2016 EX 99.02CADENCE REPORTS THIRD QUARTER 2016 CADENCE DESIGN SYSTEMS, INC … Good financial results with revenue and profitability meeting or exceeding expectations … DSO 34 days, down 1 day …...

956 KB

|

Q316 Earnings Tables_web.xlsxCondensed Consolidated Balance Sheets, October 1, 2016 and January 2, 2016 … Condensed Consolidated Statements of Cash Flows for the Nine Months Ended October 1, 2016 and October 3 …

602 KB

|

Cadence Reports Third Quarter 2016 Financial ResultsClick here for the Q3 2016 Financial Schedules … Cadence Design Systems, Inc. (NASDAQ: CDNS) today announced results for the third quarter 2016 … On a GAAP basis, Cadence recognized net …...

24 Oct 2016

|

Cadence Reference Flow with Digital and Signoff Tools Certified on Samsung’s 10nm Process TechnologyCadence today announced that its complete suite of digital and signoff tools has been certified for Samsung's PDK and Foundation Library on the second-generation of Samsung’s 10nm LPP process.

24 Oct 2016

|

Fujitsu Adopts Cadence Palladium Z1 Enterprise Emulation Platform for Post-K Supercomputer DevelopmentCadence today announced that Fujitsu has adopted the Cadence Palladium Z1 enterprise emulation platform for the development of the ARMv8-based Post-K computer.

24 Oct 2016

|

Media Alert: Cadence Enables Customer Innovation with ARM-Optimized Solutions from Chips to Boards to Systems at ARM TechCon 2016Cadence today announced it will showcase ARM-optimized solutions from chips to boards to systems at ARM TechCon 2016.

19 Oct 2016

|

Allegro® PCB Symphony Team Design 17.2 ReleaseAllegro PCB Symphony Team Design provides dynamic concurrent PCB team design for multiple PCB designers to work on the same design at the same time without any set-up requirements.

15 Oct 2016

|

Boost Your Circuit Simulation Performance with New PSpice EngineLearn how to accelerate your designs with the improvements in Cadence PCB 17.2-2016. Watch this webinar to see how the latest advancements in PCB design technology can help you to reduce back-and-forth wit...

14 Oct 2016

|

Easy-to-Use, Scalable PCB Design Tools Integrate with Enterprise-Level SystemsEngineers are doing the work of many, and managing libraries that are in chaos. How to make life easier? Manny Marcano, president and owner of EMA Design Automation, talks about how Cadence® OrCAD® and All...

13 Oct 2016

|

Unified Workflow with Allegro and OrCAD PCB Design ToolsUsing Cadence® Allegro® and OrCAD® PCB design tools, Microsemi has built a unified workflow with a database of libraries to support smooth collaboration between its different design teams. In this video, K...

13 Oct 2016

|

Radar Signal Processing for Automotive ApplicationsIn this week's Whiteboard Wednesdays video, the first of a two-part series, Pushkar Patwardhan provides an overview of radar systems in automotive applications and the different data streams that must be p...

13 Oct 2016

|

Driving Forces and Design Concerns Behind PCI Express Gen4In this week's Whiteboard Wednesdays video, the second in a two-part series, Lana Chan explores the factors that drove the development of PCIe Gen4. She also details SoC concerns that design and verificati...

11 Oct 2016

|

Cadence Delivers 10 New VIP Solutions to Accelerate Time to Market for Applications Based on Critical New StandardsCadence today announced the release of 10 new Verification IP (VIP) solutions that allow engineers to quickly verify that designs meet specifications for the latest standard protocols.

11 Oct 2016

|

Routing DDR4 Interfaces Quickly and EfficientlyComplexities of routing and tuning advance interface like DDR4 is continuing to increase. Current methods to route and tune them will not work since you are asked to do more with less. Signals in these int...

1 MB

|

IPC-2581 Consortium UpdateThe IPC-2581 Consortium has 83 PCB design and supply chain companies that are actively pushing for adoption. The companies range from systems companies to manufacturing companies and software companies tha...

2 MB

|

Managing Backdrilling from Library until Hand-off to ManufacturingAre you managing backdrilling as a post process? That’s the old school thinking. And while old habits die hard.. there is a better way to manage backdrilling from library definitions to routing to manufact...

1 MB

|

New Techniques to Address Layout Challenges of High Speed Signal RoutingThis paper reviews layout techniques, such as return path vias and tabbed routing, that address routing challenges of high-speed signal routing.

1 MB

|

MCAD-ECAD with Non-Electrical and Electrical Layers on Flex/Rigid-Flex DesignsConsumer IoT and Industrial IoT are increasing the number of flex and rigid-flex designs in the industry. At the same time, complexity of designing flex and rigid-flex designs is increasing as improvements...

1 MB

|

Allegro PSpice Simulator DatasheetCadence Allegro PSpice Simulator provides simulation technology for PCB design that offers a single, unified design environment for both simulation and PCB design. With integrated analog and event-driven d...

|

Cadence Announces Third Quarter 2016 Financial Results WebcastCadence Design Systems, Inc. (NASDAQ: CDNS) to announce third quarter 2016 financial results via webcast … You are invited to attend the third quarter 2016 financial results audio …

07 Oct 2016

|

See How DisplayPort Changes May Impact Your Next Chip DesignNavigate the evolution of the DisplayPort standard with VESA board member Craig Wiley. In this video, Craig explains the current standard and new developments that will impact SoC developers.

06 Oct 2016

|

Addressing the Challenges of Photonic IC Design Via an Integrated Electronic/Photonic Design Automation EnvironmentDescribes how an integrated electronic/photonic design automation environment addresses the challenges of photonic IC design

735 KB

|

How Much Floating Point Does Your Application Need?To address the growing needs for floating-point arithmetic in DSP algorithms, all Tensilica DSP families support floating point. In this second part of a two-part Whiteboard Wednesdays video series, we dis...

05 Oct 2016

|

Addressing Memory Characterization Capacity and Throughput Requirements with Dynamic Partitioning White PaperDynamic partitioning provides accurate and fast memory characterization enabling designers to improve design performance, reduce die area, and close correlation with manufactured silicon. This white paper ...

148 KB

|

Massively Parallel Electrically Aware Design White PaperTo address the larger designs necessary for today’s market, massively parallel computing frameworks and in-design-based parallel extraction, enabled through tools such as Cadence® Virtuoso® Layout Suite fo...

|

Cadence Recognized with Four TSMC Partner of the Year AwardsCadence recognized for joint delivery of 7nm mobile design platform, 7nm HPC design platform, InFO design solution and analog/mixed-signal IP Cadence and TSMC build on long …

27 Sep 2016

|

Cadence Announces General Availability of Tensilica Xtensa LX7 Processor Architecture, Increasing Floating-Point Scalability with 2 to 64 FLOPS/CycleCadence announced general availability of the 12th generation Tensilica Xtensa base processor architecture.

27 Sep 2016

|

Why is More Floating Point Computation Required by DSP Applications?Why is more floating-point computation required by DSP applications? More and more DSP applications use algorithms that are best realized using floating-point arithmetic. In this Whiteboard Wednesday video...

27 Sep 2016

|

Cadence and TSMC Advance 7nm FinFET Designs for Mobile and HPC PlatformsCadence today announced several important deliveries in its collaboration with TSMC to advance 7nm FinFET designs for mobile and high-performance computing (HPC) platforms.

23 Sep 2016

|

Cadence Delivers Integrated System Design Solution for TSMC InFO Packaging TechnologyCompanies collaborated to enable implementation, signoff and electro-thermal analysis tools to support customer designs using InFO packaging … For more information on the Cadence …

21 Sep 2016

|

Media Alert: Cadence President and CEO Lip-Bu Tan to Deliver Keynote at TSIA 2016Cadence announced that its president and CEO, Lip-Bu Tan, will deliver a keynote address at the TSIA on September 29, 2016, at the Ambassador Hotel in Hsinchu, Taiwan.

21 Sep 2016

|

Evolution of the PCIe StandardIn this week's Whiteboard Wednesdays video, Lana Chan explores the history of PCI Express (PCIe) and how it evolved into the de facto interconnect standard it is today.

21 Sep 2016

|

Cadence Delivers IP for Automotive Applications with TSMC’s Advanced 16nm FinFET C ProcessCadence announced a broad portfolio of interface and Denali memory IP solutions for automotive applications supporting TSMC’s 16nm FinFET Compact (16FFC) process.

20 Sep 2016

|

Cadence Delivers Rapid Adoption Kit for Fast Implementation and Signoff of New ARM Cortex-R52 CPUCadence Delivers Rapid Adoption Kit for Fast Implementation and Signoff of New ARM Cortex-R52 CPU

20 Sep 2016

|

How High-Level Synthesis Was Used to Develop an Image-Processing IP Design from C++ Source Code White PaperUsing high-level synthesis to develop image-processing IP design

|

Training Different Networks Using Hierarchical CNNIn this week's Whiteboard Wednesdays video, Michelle Mao follows up on last week's video and takes a closer look at Hierarchical CNN and how to train different networks for family and member classification...

13 Sep 2016

|

Benefits of Cadence Hierarchical CNN DesignIn this week's Whiteboard Wednesdays video, Michelle Mao talks about Cadence hierarchical CNN design for traffic sign recognition, allowing state of the art performance with less complexity. For more info...

13 Sep 2016

|

Application Optimized DDR PHYsIn this week's Whiteboard Wednesdays video, Kishore Kasamsetty takes a closer look at how designers continue to get more out of memory subsystems. The traditional one-size-fits-all DDR PHY no longer works....

13 Sep 2016

|

Radar Signal Processing Optimized for the Tensilica Fusion G3 DSPIn this week's Whiteboard Wednesday video, Pushkar Patwardhan discusses the advantages of using the Tensilica Fusion G3 DSP for implementation and optimization of radar signal processing for automotive app...

13 Sep 2016

|

Tensilica Fusion G3 DSP Features and BenefitsIn this week's Whiteboard Wednesdays video, Paul Garden provides more details on the new Tensilica Fusion G3 DSP features. He’ll discuss the benefits of the 128-bit SIMD ALU, instruction formats, auto-vect...

13 Sep 2016

|

Using Processor Clusters to Implement Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen describes how to use processor clusters to implement neural networks. This approach allows you to achieve higher frame rates, which leads to increase...

13 Sep 2016

|

Cadence Offers Industry’s First Licensable MPEG-H Audio Decoder for Tensilica HiFi DSPsCadence announced availability of the MPEG-H Audio decoder on Cadence Tensilica HiFi DSPs.

13 Sep 2016

|

Cadence Tensilica HiFi DSP Offers First processor IP Approved for Dolby AC-4 DecoderCadence announced the Dolby Laboratories' AC-4 Decoder supporting audio and video entertainment services, including ATSC 3.0 broadcasting and internet streaming on Tensilica HiFi DSPs.

13 Sep 2016

|

Power Delivery Trends from CES 2016In this week's Whiteboard Wednesdays video, Jacek Duda recaps his experience at the Consumer Electronics Show (CES) 2016. Jacek specifically highlights the power delivery function in the latest USB spec an...

12 Sep 2016

|

PCIe Gen4: Is It Coming Anytime SoonIn this week's Whiteboard Wednesdays video, Moshik Rubin discusses the history of the PCI Express (PCIe) high-speed serial interface. He highlights many of the improvements that have happened with this int...

12 Sep 2016

|

Modular VIP ArchitectureIn this week's Whiteboard Wednesdays video, Liron Stoler describes how the Cadence Verification IP (VIP) modular architecture provides important benefits to users in block and system-level verification.

12 Sep 2016

|

Memory Trends to Fit Your ApplicationIn this week’s Whiteboard Wednesdays video, Jeffrey Chung talks about the progression of DDR and LPDDR: capacity, speed, and types of applications that would be appropriate.

12 Sep 2016

|

Implementation of Multi-Link, Multi-Protocol PHYIn this week's Whiteboard Wednesdays video, William Chen deep dives into the implementation of multi-link, multi-protocol PHY.

12 Sep 2016

|

Creating an Acceleration-Ready Simulation Environment with Accelerated VIPIn this week's Whiteboard Wednesdays video, Ofer Steinberg explains how accelerated VIP can dramatically speed up verification and describes a method to simplify the application of a SystemVerilog UVM test...

09 Sep 2016

|

Key Metrics for Embedded Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen takes a closer look at the key metics for embedded neural networks and what today's devices need to do to collect this sophisticated data.

09 Sep 2016

|

Ethernet and Automotive ElectronicsIn this week's Whiteboard Wednesdays video, Sachin Dhingra follows up on last week's video by discussing Automotive Ethernet and how it fits into the four different electronic categories in a vehicle.

09 Sep 2016

|

Common Infrastructure Between Simulation VIP and Accelerated VIPIn this week's Whiteboard Wednesdays video, Arindam Guha discusses the common infrastructure between Verification IP and Accelerated Verification IP and how it assists in making the migration between simul...

09 Sep 2016

|

Gauging Signal Quality Using Eye DiagramsIn this week's Whiteboard Wednesdays video, Chung Huang summarizes his presentation from CDNLive Silicon Valley on gauging quality of signals using the eye diagram. To view his CDNLive presentation, please...

09 Sep 2016

|

Optimizing Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen discusses optimizing neural networks for low energy and high throughput applications.

09 Sep 2016

|

Mapping Convolutional Neural Networks to the Vision P5 DSPIn this week's Whiteboard Wednesday, Chris Rowen explains how convolutional neural networks (CNNs) map onto the high-performance Tensilica Vision P5 DSP. He describes the benefits that the programmability ...

09 Sep 2016

|

Introduction to the new Tensilica Fusion G3 DSPIn this week's Whiteboard Wednesdays video, Paul Garden provides an introduction to the new Tensilica Fusion G3 DSP for automotive, mobile, industrial and general embedded DSP applications. He’ll discuss t...

09 Sep 2016

|

Assertion-Based Verification IPIn this week's Whiteboard Wednesdays video, Tom Hackett takes a closer look at assertion-based Verification IP (VIP), what it is, and why it is useful.

09 Sep 2016

|

Reusable Data-Driven Verification Using TLM 2.0In this week's Whiteboard Wednesdays, Zeev Kirshenbaum describes a method for creating protocol-independent stimulus using verification IP along with SystemVerilog TLM 2.0 extensions. This makes interface...

09 Sep 2016

|

Media Alert: Cadence to Showcase Latest PCB Design Tools at PCB West 2016Cadence will be featuring its latestOrCAD® and Allegro® technologies at PCB West 2016.

07 Sep 2016

|

Applying Deep Learning to Our Daily LivesIn this week's Whiteboard Wednesdays video Samer Hijazi discusses bringing deep learning to embedded devices.

07 Sep 2016

|

SSD Controller Basics and TrendsIn this week's Whiteboard Wednesdays video, Neil Robinson talks about SSD Controllers - showing the functionality basics and trends for increasing the performance and lowering the energy consumed while add...

07 Sep 2016

|

SSD Controllers with Tensilica ProcessorsIn this week's Whiteboard Wednesday, Neil Robinson follows up on last week's “SSD Controller Basics and Trends” video to show how optimizing Tensilica processors for use in SSD controllers meets the high p...

07 Sep 2016

|

Prof. Michael Huebner (Ruhr University of Bochum) – Cadence Academic NetworkProf. Dr. -Ing. Michael Huebner, Chair for Embedded Systems in Information Technology (ESIT) at the Ruhr-University of Bochum talks about Ruhr Univeristy, the ways in which he uses Cadence tools in his res...

07 Sep 2016

|

Sweepstake-Rules-5th-September-2016.pdfSURVEY SWEEPSTAKES PRIZE DRAW (THE “PROMOTION … Eligibility: This Promotion is open to legal residents of the fifty United States and the District of Columbia (together “USA”), EU …

211 KB

|

Cadence Senior Vice President and Chief Financial Officer Geoff Ribar to Present at the Deutsche Bank Technology ConferenceGeoff Ribar, senior vice president and chief financial officer, Cadence Design Systems, Inc. (NASDAQ: CDNS … Ribar will participate in a fireside chat and question and answer session …

29 Aug 2016

|

Floating-Point Core of Tensilica Vision P5 DSPIn this week's Whiteboard Wednesdays video, Dennis Crespo explains the optional vector floating-point core specifications of the Tensilica Vision P5 DSP.

25 Aug 2016

|

Hardent: Lower Bandwidth, Higher Quality Video Transfer with IPDisplay resolution in consumer products has been increasing by a factor of 2X year over year, while transport technologies like PHYs and cabling have been experiencing yearly speed increases of about 20%. ...

25 Aug 2016

|

IC Package Assessment Demo - Allegro Sigrity SI 16.6125 Aug 2016

|

Tensilica Vision P6 DSP Enhanced for CNNIn this week's Whiteboard Wednesdays video, Dennis Crespo discusses the significant enhancements to the Tensilica Vision P6 DSP for Convolutional Neural Networks (CNN).

23 Aug 2016

|

The Future of Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen looks at the future of neural networks and the key emerging trends.

23 Aug 2016

|

The Latest on the MIPI CSI-2 2.0 ProtocolIn this week's Whiteboard Wednesdays video, Moshik Ruben takes a closer look at the MIPI CSI-2 2.0 protocol and how this latest specification addresses today's pressing issues such as bandwidth, internet o...

23 Aug 2016

|

Ubiquitous USB Interface EvolutionIn this week's Whiteboard Wednesdays video, Arif Kahn details the evolution of the USB interface from USB 1.0 to today's latest USB Type-C interface.

23 Aug 2016

|

Understanding the Computational Activity Behind Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen discusses the inter-workings of neural networks, which are applied to a variety of data types for pattern recognition. Hear Chris explain what is hap...

23 Aug 2016

|

Vision Systems and Neural NetworksIn this week's Whiteboard Wednesdays video, Chris Rowen discusses using neural networks as part of vision systems.

23 Aug 2016

|

Advantages of the MIPI I3C InterfaceIn this week's Whiteboard Wednesdays video, Alex Passi explains the advantages provided by the new MIPI I3C interface. With I3C, mobile device sensors can transmit data faster, with lower power and simpler...

23 Aug 2016

|

Where Ethernet is Used in Automotive ElectronicsIn this week's Whiteboard Wednesdays video, Sachin Dhingra takes a closer look at the different categories that implement automotive Ethernet and their importance to the driving experience.

23 Aug 2016

|

Irida Labs’ NoiseSweeper and EnLight Software Now Available on Cadence Tensilica Imaging/Vision DSPsCadence and Irida Labs announced that Irida Labs’ IRIS-EnLight and IRIS-NoiseSweeper technologies are now available on the Tensilica Vision family of digital signal processors (DSPs).

23 Aug 2016

|

Implementation of Higher Speed PCIe Gen4 IPIn this week's Whiteboard Wednesday's video, Gopi Krishnamurthy highlights how Cadence implements the higher speeds of PCI Express (PCIe) Gen4 into the PCIe controller and PHY IP.

23 Aug 2016

|

Corporate Governance GuidelinesCadence Corporate Governance Guidelines

|

Relationships Between USB SpecsIn this week's Whiteboard Wednesdays video, Jacek Duda describes the relationships between USB Type-C, USB 3.1, and Power Delivery specificationss, and gives examples of applications for each.

23 Aug 2016

|

Protium Rapid Prototyping PlatformProtium Rapid Prototyping Platform - FPGA-based Prototyping Done Right

19 Aug 2016

|

Protium Rapid Prototyping Platform DAC WebinarProtium Rapid Prototyping Platform - Productivity and Ease-of-Use in FPGA-based Prototyping

19 Aug 2016

|

Reducing Cost, Size of PCBs with Embedded Technologies and Cadence Layout ToolsDialog Semiconductor faced a potentially daunting challenge: reduce the size and cost of its PCBs via embedded passive devices at the substrate level. The company needed a tool that could help migrate from...

18 Aug 2016

|

Sigrity Tech Tip: How IC Package Designers Can Find and Fix Electrical ProblemsAllegro® Package Designer (http://goo.gl/YvOZYn) and Sigrity™ XtractIM™ technology (http://goo.gl/Vxs94Y) from Cadence are demonstrated. Sigrity technologists guide you step by step on how IC Package Desig...

18 Aug 2016

|

SiriusXM Simulates DDR3 Interfaces with Sigrity ToolsAt SiriusXM, engineers develop satellite radio baseband devices that use higher density and higher frequency DDR3 memory. The company's latest design more than doubled the density and clock rate of previou...

18 Aug 2016

|

Nexus Interposers and Cadence Tools Enhance DDRx DesignsAt Nexus Technology, Joe Socha, signal integrity engineer, is responsible for analyzing tiny PCBs that are used as interposers between memory devices and their target systems. Probing memory devices can be...

18 Aug 2016

|

Lattice Saves Millions, Avoids Respins and Product Delays with Sigrity ToolsLattice is a global leader in delivering ultra-low power FPGAs for manufacturers of smartphones, small cell networking equipment, and industrial applications. For its customer base, fast time to market, lo...

18 Aug 2016

|

Parallel Systems, providing world leading EDA software, sales, support and training since 1997