Cadence Customer Testimonials

The Cadence solution enables us to enter up to 99 percent of signals in table format, which, along with improved analytics and a unique integrated environment, reduces our PCB development time by 80 percent

- Gisbert Thomke, Group Leader, IBM R&D Lab

“It’s just a pleasure to route and design these boards. We actually broke our previous tool, component-wise and net-wise. .. Now doing these really tight, difficult boards with the Allegro tools is great,”

- Boris Nevelev, Imagine Communications (View PDF success story)

The Cadence Allegro system interconnect design platform has significantly changed our high-speed board design process. Our partnership with Cadence has allowed us to decrease our time to market and increase our confidence in first pass success for our designs. Projects that used to take quarters to complete now take only months, and we trust that the first spins will come back functioning as intended.

- Tim Kent, Vice President of Engineering, Liquid Computing Corp.

During the design of the GS0036, we at Gnodal found the new Design Replicate feature in Allegro helped to considerably reduce our timescales. Initially we were able to use the feature to reproduce placements of similar circuits from previous designs in our placement studies. We then used it to very easily repeat the placement and routing of complex circuits and finally it allowed us to have more than one layout engineer working on the design simultaneously. This feature has helped Gnodal target an aggressive timescale on an important design.

- Jim Corke - Gnodal

As a designer I have used similar features in medium to high end CAD systems before with some level of success. With this powerful enhancement to the routing functionality, Cadence have managed to up the game and take PCB design to next level of evolution. I can see myself using these key features a lot within our forthcoming designs and of course ultimately, it will save us a lot of time and effort into getting what we want done quickly and effectively.

Joe Kotvics Acano

If you ever need a reference from a small customer, I am very happy to vouch for the professionalism of your team. I am really happy with the way your team managed the whole process of selling the OrCAD suite to me, I just wish to express my thanks

- Florin Stroiescu - Strasmax

As a result of using the OrCAD solutions for PCB development, "home2net" has achieved a 30% faster development cycle, has reduced costs by 15%, and can readily meet its stringent timeto-market goals. - Home2Net Success Story

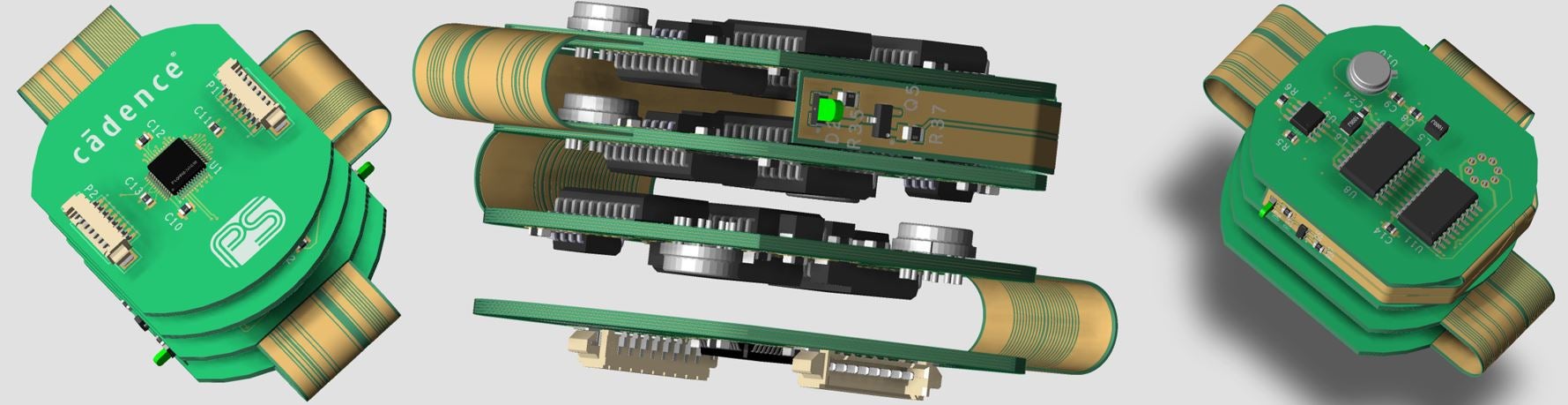

"The majority of our PCB layouts are complex, highly constrained designs that demand a signal integrity-based design-flow. The Cadence Allegro v16 schematic entry, PCB layout and SI analysis tools, provided through Parallel-Systems, give us the ability to handle the most challenging designs and maximise our competitive edge. Continual feature development, expert technical support and a high level of productivity are just three reasons why weve built our company around Cadence Allegro."

- Chris Halford, Advanced Layout Solutions

We chose PSpice for several reasons. The availability and selection of models is vast and updated online. Time saving features like the Checkpoint Restart allows me to store simulation states at various time-points and then restart simulations from any of the simulation states. All in all its a great product and is a key part of our design team. I can see why it is the industry standard

- Paul Overton - Senior Electrical Engineer - Viper Subsea

With an integrated tool flow in Cadence Allegro, we have seen increased productivity for PCB design. Now that our designs are heavily constrained, the PCB design might be expected to take a lot longer. However, the design checking process is so much shorter, that the overall time is less. More importantly, with all the necessary nets constrained in the schematic, the chances of a PCB revision for signal integrity reasons have been vastly Reduced. Cadence Allegro design entry HDL has had advanced features (such as constraint editor) for a long time, and it has been stable for us. We have not seen any bugs with the software. This compares favourably with our experience with competitive tools which promised good things, but in VMETROs experience were not stable.

- Hugh Tarver Engineering manager at VMETRO Ltd.

Cadence Allegro has helped us push the technological envelope for designing layouts using multi site BGA, high density, RF, digital and high layer counts. As a leader in ATE hardware fixtures, we have found the alliance between Cadence and Parallel Systems a useful synergy, where both companies have given their expert advice towards new software tools, updates and training programmes, helping us to make sure that we keep ahead of our game.

- Nigel Rowe Shane Consultants Limited

I am thoroughly impressed with the Orcad Unison package as a whole; the software has proved to cater for all my demands as a design engineer. Complex and large-scale schematics are easily realised and intuitively managed. The integration between the PCB layout and the schematic is seamless and enormously simplifies the development process. The SPECCTRA PCB auto-router is both powerful and simple to use. This has resulted in a faster time to market compared with previous software packages.

- ZaferJarrah - Hybrid Instruments UK

OrCAD PCB Designer with PSpice provides my business with an integrated development tool that works from the first schematic concept, through simulation and on to product realisation - all straight out of the box. It's even useful during hardware debug as the link between the Capture and PCB Designer allows for quick and easy track tracing. Add in the effective and intelligent customer support and you have a first class package. OrCAD Capture allows me to get on with the job of designing electronics without having to fight my software. From jobs with 10 components on a single sheet through to complex hierarchical systems with 30 schematic pages, Capture has handled it all

- Craig Britton Supply Design

We purchased OrCAD Layout and it was good value for money. We felt that it was not meeting the requirements for todays high speed technology and complex designs, and were pleased to hear that the product was to be upgraded. The new, OrCAD PCB Designer utilises the highly regarded Allegro PCB Design Editor which has brought greater efficiency in component placement and routing; we were very impressed with the way it handled routing in planes/copper pouring etc. Library management is significantly improved and there is a general feeling of increased productivity. It is fully compatible with the high end Allegro product range

Jim Hurford. Dayford Designs.

OrCAD PCB Designer is a great tool for a service bureau like us. With PCB Designer, we can use OrCAD Capture, the popular schematic entry tool used by many of our customers. We also do PCB layout based on the solid Allegro database format. This allows us to reuse designs, if necessary, and addresses high-speed issues within the Allegro Environment.

- Ronald Weber, PCB designer at DesConTec

Shaving Weeks Off PCB Design Cycle Via Auto-Routing Case Study

Cadence and Faraday Technology Case Study

Cadence and IN2P3 Success Story

Imagine Communications and Cadence Success StoryDesigning Complex, High-Speed Boards with Fewer Re-Spins

|

Altair and Cadence Success StoryWith Cadence analog IP, Altair is able to develop low-power analog designs in shorter timeframes without compromising performance.

149 KB

|

Cadence and NetSpeed Success StoryNetSpeed Systems provides scalable, coherent, on-chip network (NoC) IPs to system-on-chip (SoC) designers. Palladium XP platform is an integral component of NetSpeed’s overall solution for verification cha...

272 KB

|

Cadence and Tait CommunicationsTait Communications designs, develops, manufactures, tests, deploys, supports, and manages innovative digital wireless communications environments. By using the Allegro PCB Library Workbench Tait engineers...

195 KB

|

Moving to UVM-MS to Meet Coverage Goals Case StudyBy migrating from a module-based mixed-signal verification environment to UVM, Freescale Semiconductor gained a top-level mixed-signal verification framework that supports constrained random verification.

268 KB

|

Faster Hardware Verification and Software Validation for Supercomputers Success StoryCadence Palladium XP system helped Fujitsu achieve 300% faster post-silicon bring up.

193 KB

|

Shaving Weeks Off PCB Design Cycle Via Auto-Routing Case StudyPolycom is a long-time Cadence customer who is using tools including OrCAD Capture CIS for schematic design entry and synchronization/validation of parts data and Allegro PCB Designer for constraint-dr...

191 KB

|

4X Faster Timing Closure on High-Speed Interfaces with Allegro TimingVision Environment Case StudyCavium team implemented the Allegro TimingVision environment, available within the Allegro PCB Designer constraint-driven PCB design environment - High-Speed Option. The team also uses Allegro Constraint M...

483 KB

|

Cadence and STMicroelectronics Success StoryBy automating its RTL ECOs with Encounter Conformal ECO Designer has enabled the ST’s APG division to stay on top of customer needs in its high-pressure industry.

479 KB

|

Cadence and Ricoh Success StoryThe Incisive vManager and MDV solution provided enough new approaches and productivity results for Ricoh for the engineers to call the project a success.

313 KB

|

Cadence and Pegatron Success StoryThe Pegatron team used the Timing Vision feature of Allegro PCB Designer to gain a sharper view of the constraint condition of its design.

405 KB

|

Cadence and VIA Telecom Success StoryVIA Telecom has adapted the Cadence low-power flow to its process for small mixed-signal devices. To further increase productivity, the team will evaluate Cadence Tempus Timing Signoff Solution, which deli...

400 KB

|

Cadence and Faraday Technology Case StudyFaraday utilized many solutions from Cadence, including Verification IP (VIP), Encounter Digital Implementation Incisive verification platform and Sigrity packaging and PCB signal and power analysis solut...

538 KB

|

Cadence and Texas Instruments Success StoryCadence advanced simulation and characterization solutions helped the TI EDM team meet its cycle-time and capacity requirements for compiler memory design, verification, and characterization.

362 KB

|

Cadence and STMicroelectronics Success StorySTMicroelectronics STxP70 processor technology offers a costeffective, real-time optimized, 32-bit RISC system. It can be integrated into systems on chip (SoCs) in individual or multiprocessor (MP) configu...

463 KB

|

Cadence and Melexis Success StoryMelexis Microelectronic Integrated Systems, headquartered in Belgium develops advanced mixed-signal semiconductors, sensor ICs, and programmable sensor IC systems for the automotive electronics industry

610 KB

|

Cadence and STMicroelectronics Success StorySTMicroelectronics is a world leader in providing semiconductor solutions for a wide range of application areas that make a positive impact on peoples lives, today and in the future.

465 KB

|

Cadence and IN2P3 Success StoryAllegro FPGA System Planner provides the IN2P3 teams with the flexibility to more efficiently upgrade or reconfigure their FPGA-based systems, without having to start from scratch.

477 KB

|

Cadence and Uniquify Success StoryUniquify is a provider of leading-edge system-on-chip (SoC) design and manufacturing, and intellectual property (IP) solutions.

339 KB

|

Cadence and RivieraWaves Success StoryIncisive verification solutions enabled RivieraWaves to easily migrate from OVM to UVM for its next-generation Bluetooth 4.1 IP designs. This enabled the company to increase automation and enable its cus...

487 KB

|

Cadence and Siemens Healthcare Success StoryIncisive toolflow has enabled Siemens to effectively and efficiently capture and analyze all coverage. Using Cadence solutions has been so successful that Siemens plans to use the new constrained-random ve...

303 KB

|

Texas Instruments and Cadence Verification Success StoryBy combining Palladium XP DPA with Encounter Power System TI achieved close correlation between the architects power estimation and actual silicon power consumption measurements enabling the company to del...

468 KB

|

Cadence and Nufront Success StoryUsing hot-swap technology Palladium XP increased Nufronts productivity by enabling users to transition among simulation, simulation acceleration, and emulation environments at runtime without re-compilatio...

310 KB

|

Cadence Incisive Enterprise Simulator and Samsung Success StorySamsung and Cadence implemented a structured approach for the verification of Samsung's mobile application processor Exynos, as the chips grow through 150 million gates.

575 KB

|

Cadence and Sharp Success StoryUsing the Encounter RTL-to-GDSII flow and its integrated product technologies, Sharp achieved a 2x faster turnaround time compared to its previous digital flow.

305 KB

|

Cadence and Rohde & Schwarz Success StoryRohde & Schwarz IC design engineers use Spectre Accelerated Parallel Simulator (APS) from Cadence to perform complex simulations required to meet the demanding specifications of high-frequency circuits.

374 KB

|

Cadence and Faraday Success StoryUsing Conformal ECO Designer Faraday has developed a fast and efficient ECO flow to handle functional logic changes. The Cadence solution offers improved predictability, faster process time, high-quality...

386 KB

|

Cadence and Samsung Success StorySamsungs new PCI Express-based SSD needed hundreds of times greater performance than their simulation environment could provide. Using Cadence PCI Express AVIP running on the Palladium XP platform, Sams...

290 KB

|

Cadence and Fujitsu Success StoryFujitsu Microelectronics Limited, a global leader in microelectronics for computers and communications devices, has now successfully developed the first 65nm SoC for mobile WiMAX applications.

600 KB

|

Cadence and Fuji Electric Success StoryFuji Electric (FE), a global company based in Japan, supplies advanced, innovative power device and power modules that save energy while offering high performance.

426 KB

|

Cadence and STMicroelectronics Success StorySTMicroelectronics (ST) is a world-leading integrated device manufacturer providing semiconductor solutions for all electronics segments.

462 KB

|

Cadence and Newport Media Success StoryNewport Media Pinpoints Design Bugs Earlier with Cadence Assertion Based VIP and Incisive Formal Verifier.

520 KB

|

Cadence and QLogic Success StoryQLogic is a leader in converged networking, enterprise Ethernet, and storage area networking (SAN) products. To meet its stringent time-to-market requirements for the network switch, QLogic used Cadence P...

553 KB

|

Cadence and Texas Instruments Success StoryTI followed the Cadence Digital Mixed Signal (DMS) methodology and extend the successful MDV verification methodology into the analog and mixed-signal domains.

982 KB

|

Cadence and Xilinx Success StoryIncisive Enterprise Simulator with Specman technology provides Xilinx increased productivity for both hard and soft IP development, and it improves overall IP quality.

428 KB

|

Cadence and Renesas Success StoryCadence Encounter Timing System Helps Renesas Reduce Pessimistic Compensation in 65nm and Below Designs

842 KB

|

Cadence and Teradyne Success StoryTeradyne Improves Productivity and Quality of Silicon Using Cadence Virtuoso Multi-Mode Simulation

1 MB

|

Cadence and Realtek Success StoryRealtek Reduces Design Cycle Time on Communications SoC Using Virtuoso Transistor-Level to Full-Chip Mixed-Signal Verification

327 KB

|

Cadence and Multigig Success StoryMultigig Implements Full Cadence-Based Simulation Flow for High- Precision RF and Mixed-Signal ICs.

552 KB

|

Cadence and Spansion Success StorySpansion - a leading provider of Flash memory technology for electronics systems - about using Cadence Virtuoso custom design technologies.

715 KB

|