Sigrity Optimize PI

Sign off with confidence

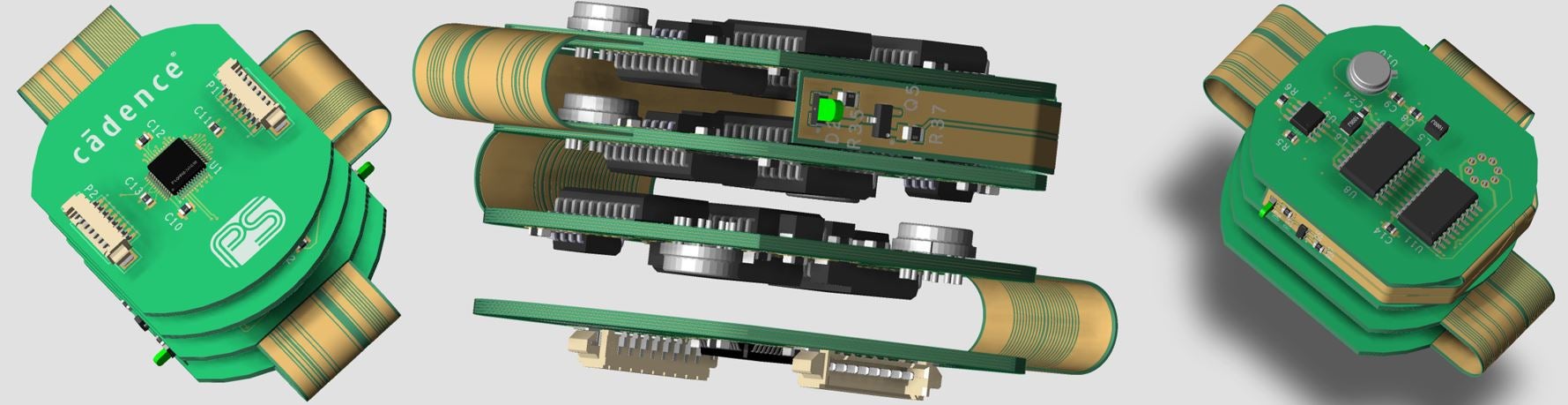

Sigrity™ OptimizePI™ technology enables design teams to balance decoupling capacitor (decap) cost and performance for PCBs and IC packages. Decap cost savings of 15% to 50% are typical. Using OptimizePI technology, you can analyze and ensure high performance for the power delivery system (PDS) at both a system and component level.

OptimizePI technology is built on proven Cadence hybrid electromagnetic circuit analysis technology in combination with the unique Sigrity optimization engine to quickly pinpoint the best possible decap selections and placement locations.

Features

- Automatically selects and places decoupling capacitors

- Eliminates decap over-design for PCBs and IC packages

- Reduces PDS cost for new designs and post-production products

- Develops effective decap guidelines for packaged components

- Recaptures design area by eliminating unnecessary decaps

- Assesses PDS cost vs. performance tradeoffs interactively

- Optimizes a PDS across the board/package interface

- Creates lowest cost/best performance decap placement tables

- Identifies both the number and locations for EMI decaps

Benefits

- Quantifiable decap cost savings without PDS performance risk

- Uniquely flexible and fully automated environment for analyzing cost vs. performance

- Robust and proven underlying hybrid EM/circuit analysis technology

- Intuitive and interactive visualization of PDS performance

- Simple to set up for pre- and post-layout decap optimization

- Unique device impedance and EMI resonance checking

- Ability to support large designs that include both package and board data

- Optimized for flows with Cadence® SiP Layout, Allegro® Package Designer, and Allegro PCB Designer

- Readily used in Mentor, Zuken, and Altium flows, accepting a mix of CAD databases where needed for multi-structure design support