The OrCAD® 17.2-2016 release introduced new capabilities for OrCAD Capture, PSpice® Designer, and PCB Designer 17.2-2016 that address challenges with flex and rigid-flex design as well as mixed-signal simulation complexities in IoT, wearables, and wireless mobile devices. This latest release reduces PCB development time by addressing the need to design reliable circuits for smaller, more compact devices.

Please note all "in Maintenance" customer will receive their new 17.2 2016 license on Tuesday 10th May 2016

To enable a faster and more efficient flex and rigid-flex design creation critical to IoT, wearables and wireless devices, the OrCAD 17.2-2016 portfolio enables several new capabilities for flex and rigid flex design to minimize design iterations. Key flex and rigid flex features include:

- Stack-up by zone for flex and rigid-flex designs

- Inter-layer checks for rigid-flex designs

- Contour and arc-aware routing

In the OrCAD PCB Designer 17.2-2016 release, the Cross-Section Editor has been redesigned to leverage the underlying spreadsheet technology found in the Constraint Manager. It offers a one-stop shop for features that require the cross section for their setup, such as dynamic unused pad suppression and embedded component design. The Cross-Section Editor has been enhanced to support multiple stackups for rigid-flex design, each capable of supporting conductor and non-conductor layers such as Soldermask and Coverlay.

A new Padstack Editor has been introduced in OrCAD PCB Editor 17.2-2016 to ease padstack creation through a new modern user interface. In addition to supporting new pad geometries, drill types, additional attributes, and additional mask layers ability to define keep-outs within the padstack with complex geometries for all objects, the new capabilities allow PCB librarians to help PCB designers streamline the design process for complex padstacks, and also the commonly used padstacks.

The OrCAD PCB Designer 17.2-2016 release also include new features or enhancements targeted towards improving PCB editors’ productivity and ease-of-use. Other new features include: Via2via Line Fattening (HDI), Display Segments Over Voids, Layer Set Based Routing, Diff Pair Routing and DRC, Full Xnet Support, Gloss Commands, Contour Routing, and many more!

The Graphical Design Difference Viewer is a powerful, real-time, design difference, visual review utility in OrCAD Capture with the ability to perform logical as well as graphical comparisons on a page-by-page basis. The Graphical Design Difference Viewer generates an interactive single-report HTML file that is platform and tool independent, a unique viewing feature to identify the differences leading to changes in circuit behavior as well as differences based on individual object level, thereby helping address the specialized needs of the users.

With the newly introduced Advanced Annotation feature supported by OrCAD Capture, users can assign reference ranges hierarchically by automatically assigning values and perform annotation on the whole design, on hierarchy block at any level, page and property block, giving them complete control over their component annotation process in the design cycle.

The new virtual prototyping functionality introduced in PSpice helps electrical engineers overcome design challenges by automating the code generation for multi-level abstraction models written in C/C++ and SystemC. This functionality assists them in generating code requiring limited coding capabilities by design engineers and thereby making the process of virtual prototyping extremely convenient and easy.

OrCAD Capture - 17.2-2016 Release

- Design Difference Viewer: New feature to perform logical and graphical comparisons between two designs, two schematic folders or two schematic pages and view the difference report in the form of a portable HTML format. (Watch Demo Video)

- Advanced Annotation: The new advanced annotation feature lets users annotate multiple schematic pages at a time giving them complete control over their component annotation process in the design cycle. (Watch Demo Video)

- Open Demo Design: The new Open Demo Design browser gives access to more than 150 demo designs made available from different locations, collated together to help users better understand Capture, Capture CIS and Capture _ PSpice Flow.

- Export - Import XML: OrCAD Capture provides you the capability to convert Capture designs to XML format and vise-versa based on the requirement.

- ISCF Export : Introducing direct ISCF (Intel Schematic Connectivity Format) feature for automating Intel-based design reviews to export hierarchical schematic designs in an Intel-approved format helping users optimize the design review process.

- PDF Export: The new PDF export functionality lets users export Capture design as PDF file and provides intelligent design information.

- Extended Preferences setup: The extended Preferences Setup window allows you to modify additional application settings in OrCAD Catpure like Command Shell, design and libraries, design rule check, CIS, NetGroup, NetList and Schematic.

OrCAD PCB Designer - 17.2-2016 Release

- Rigid Flex (Watch Demo Video)

- Stack up by zone: The new feature improves MCAD-ECAD co-design and provides faster, easier definition of stack-ups for rigid-flex rigid designs.

- Inter design layer checks: The new inter layer functionality provides ability to check geometries between two different class/ subclasses for flex and rigid flex designs.

- Arc routing - A new prototype feature to provide more efficient method to add routing during Add Connect by following an existing connect line or a route keep-in.

- Cross section editor- Redesigned Cross Section Editor based on the spreadsheet technology found in Constraint Manager to provide one stop shop for features requiring cross section for their setup.

- New padstack editor – Introducing modern user interface for convenient padstack creation with addition of new geometries and support for counter-bore/ counter-sink definitions and several new drill features.

- Shape Edit Application Mode –Introducing new functionality that is a fine tuning editing environment to increase efficiency with shape boundary editing and simplifying actions such as sliding a shape edge or adding a notch etc.

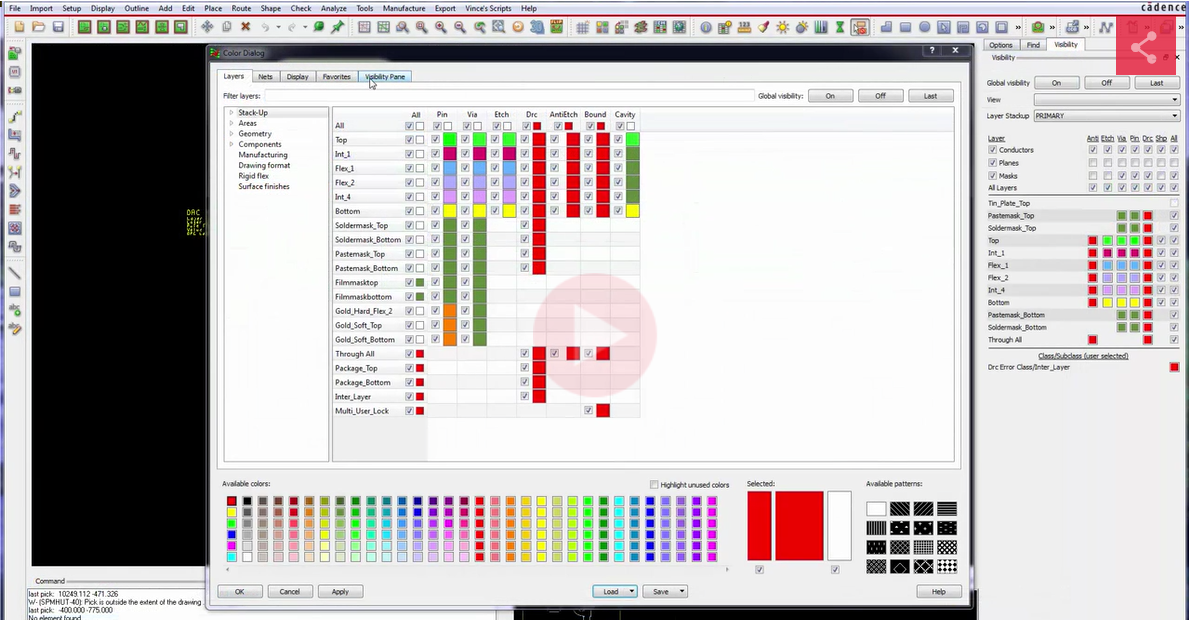

- Color and Visibility enhancements – The Color Dialog box has been enhanced for better efficiency and ease of use for designers and the Visibility pane now provides access and control over layers other than the conductor layers.

- 64 Bit Support – Now available support for 64 bit OS with increase in memory size from 4GB to 18 Quintillion and support for Database sizes upto 3GB.

- More gains in performance for CPU intensive applications.

- Display segment over voids – A new command Segment Over Voids detects cline segments crossing adjacent plane layer voids. (Watch Demo Video)

- Spread Line between Voids – New command to provide semi-automatic solution to spread channel based clines with respect to adjacent plane layer voids.

- Via2Via Line Fattening- Users can increase line width between vias based on their definition of edge to edge clearance by using the “Line fattening” utility. (Watch Demo Video)

- Contour routing- Now available in both single and mutli-routing modes, contour hugging locks the current route to either the route keepin or adjacent cline.

- Group routing – User can now perform group routing by window selecting around a group of objects(Clines, Vias, Pins, Rats) and be able to change the control trace from its initial location to user defined and go into single trace mode to complete routes.

- Gloss Commands – Richer set of gloss commands like Eliminate Vias, Convert corners to ARC, Fillet and Taper traces and many more now available in OrCAD PCB Designer.

- Differential Pair Routing and DRC – Users can now define physical and electrical rules for Differential pairs complemented by routing support.

- Layer Set DRC and Routing – The new layer set functionality insures layer constrained nets are routed to wiring requirements by ‘locking routes’ to within the appropriate layer set(s) for the net based objects. (Watch Demo Video)

OrCAD PSpice Designer - 17.2-2016 Release

- Virtual Prototyping: New functionality for automating the code generation for multilevel abstraction models written in C/C++, and SystemC, VerilogA-ADMS, and a set of behavioral analog devices and controlled sources. (Watch Demo Video)

- 64 Bit Simulation Engine and Result Analysis – Leverage full potential of compute platform to perform simulation and waveform analysis on extremely large designs.

- New functions for Behavioral models – a set of Delay() functions to introduce delay in behavioral models or controlled sources.

- New Models – Models for TinySwitch-III family devices and new Optocoupler devices have been added

- Support for TCL 8.6 - In 17.2 release Capture and PSpice support TCL 8.6.

What's New in Allegro 17.2 2016 ?

The Cadence® Allegro® 17.2-2016 release enables a more predictable and shorter design cycle. The portfolio features comprehensive in-design inter-layer checking technology that minimizes design-check-redesign iterations and a new dynamic concurrent-team-design capability that accelerates product creation time by up to 50 percent. Utilizing material inlay fabrication techniques, these new capabilities can reduce material costs by up to 25 percent. In addition, embedded Sigrity™ technology now ensures critical signals meet performance criteria and power integrity (PI) for PCB designers addressing power delivery and IR drop issues efficiently, eliminating time-consuming iterations with PI experts.

New Allegro PCB Editor Capabilities

New capabilities for flex and rigid-flex designs

- Stack-Up by Zone for Flex and Rigid-Flex Designs

Multiple zones can be created using the new Cross-Section Editor to represent rigid-flex-rigid PCBs. The stack-up by zone feature provides faster, easier definition of stack ups for rigid-flex-rigid designs and improves MCAD-ECAD co-design. - Inter-Layer Checks for Rigid-Flex Design

The Allegro PCB Editor 17.2-2016 release introduces new in-design inter-layer checks for flex and rigid-flex that save manual effort and ensure all rules for advance flex designs are adhered to, avoiding many design-check-redesign iterations. - Enhanced Contour, Arc-Aware Routing

Enhanced Contour is a more efficient method to add routing during Add Connect by following an existing connect line or a route keep-in, which will save time for PCB designers working on flex designs.

Watch Video Demo »

Learn more »

Cross-Section Editor

The Cross-Section Editor has been redesigned, leveraging the underlying spreadsheet technology found in Constraint Manager. It offers one-stop shop for features that require the cross section for their setup, such as dynamic unused pad suppression and embedded component design.

Dynamic concurrent team design

The New Allegro dynamic concurrent-team-design capability focuses on shortening the largest portion of the PCB layout design cycle. It provides dynamic concurrent PCB team design for multiple PCB designers to work on the same design at the same time without any set-up requirements. In addition, new features—including interactive etch-editing capabilities, Allegro TimingVision™ technology, auto-interactive delay, and phase-tuning capabilities—provide proven time reductions to route advanced high-speed interfaces such as DDRx and PCI Express® (PCIe®) by up to 80 percent.

New Padstack Editor

A new Padstack Editor eases padstack creation through a new modern user interface. New features include the padstack designer, padstack usage types, pad geometries, and several new drill features.

Expanded in-design rules for backdrill vias

Many improvements have been made to the backdrill process to assist PCB designers in managing the backdrill vias/padstacks, route around the backdrill vias/padstacks with accurate DRCs, and real-time feedback.

Tabbed routing

Tabbed routing is a new routing strategy in which trapezoidal shapes called tabs are added to parallel traces to control impedance in the pin-field/breakout region and crosstalk in open-field region. This method enables longer trace lengths and use of smaller trace spacing. Tabbed routing is used for impedance control and to manage crosstalk in critical signals, enhancing signal quality and improving route channel utilization.

Watch Video Demo »

Learn more »

Return path management through custom via structures

The Allegro 17.2-2016 release enhances the six via structures for managing return paths for critical differential signals during Add Connect by allowing users to create using Allegro PCB Editor, validate using proven Sigrity technology, and instantiate a custom return path via structure during Add Connect.

Ease-of-use improvements in Allegro PCB Editor

- Visibility Pane—Access to Mask Layers and Zones

The Visibility Pane has been enhanced to allow designers access and control of layer content more quickly and more efficiently. - Shape Edit Application Mode

The Shape Edit Application Mode is a tuned editing environment primarily designed to increase efficiency with shape boundary editing. - Constraint Manager Improvements

Many ease-of-use and productivity improvements have been made to Allegro Constraint Manager.

New Allegro Front-End Design Capabilities

Support for watermark in generated PDF file in Allegro Design Authoring DE-HDL

Users can now embed a watermark such as “First Prototype,” “Confidential,” or “Review Copy” in the generated PDF file.

Tag-based ECSet mapping in Allegro Design Authoring DE-HDL

ECSet nodes now support tags (pin parameter), which can be used to uniquely identify a pin and remove any ambiguity.

Port Groups in Allegro Design Authoring DE-HDL

Net Groups can be pushed across different levels of hierarchy by creating a Port Group. The Port Group is made available to higher-level blocks through the hierarchical block symbol where they appear with a new Pin Shape for unique identification.

Import of pin delay properties in front end in Allegro Design Authoring DE-HDL

A new DE-HDL console command is now provided to import a file containing the pin delay values that can be used to define the complete delay for pin pairs. The format of this file is exactly the same as that one used for import/export by PCB Editor.

Support for page-level team design with Allegro Design Authoring Team Design Option

A significant advancement in Allegro design management features is the ability to manage designs at the page level, for both hierarchical and flat designs.

Graphical Design Difference Viewer in Allegro Design Entry Capture

Graphical Design Difference Viewer is a powerful, real-time, design difference, visual review utility in Allegro Design Entry Capture with the ability to perform logical as well as graphical comparisons on a page-by-page basis.

Advanced Annotation in Allegro Design Entry Capture

With the newly introduced Advanced Annotation feature supported by Allegro Design Entry Capture, users can assign reference ranges hierarchically by automatically assigning values and perform annotation on the whole design, on hierarchy block at any level.

PSpice virtual prototyping in Allegro AMS Simulator

New functionality introduced in PSpice® helps to overcome design challenges for electrical engineers by automating the code generation for multilevel abstraction models written in C/C++, SystemC.

New pin assignment options in FPGA System Planner

A new “FSP Bundle Swap” option is available. If the two bundles are the same size, the PCB designer can select the bundles and ask the FPGA System Planner engine to swap them, pin for pin. FPGA System Planner 17.2 also offers three new manual pin-swapping algorithms: show all destination pins, show all destination pins in the same bank, and two-pin selection.

Create custom connectors with user-defined groups and pin types in FPGA System Planner

Users can now create complex connector models with user-defined pin types and signal group capabilities.

Optimize multiple, separate FPGA System Planner designs in Allegro PCB Editor

When selecting the FPGA System Planner project in Allegro PCB Editor, the PCB designer can select any one of several FPGA System Planner projects that are part of the master design.

Other enhancements

- New “Targeted Pin View” option in the Design Connectivity window

- Enhanced net name template

- Instance-level targeted pin function override

- Hyperlinked error messages when checking protocols, rules, and virtual interfaces

New Allegro EDM Capabilities

Team design capability integrated into Allegro DE-HDL

All of the team design functionality is now built directly into Allegro Design Authoring DE-HDL. Team members can stay within DE-HDL to check out/in designs using menus integrated into the DE-HDL hierarchy viewer or by using a design dashboard. And users have the ability to manage designs at the page level, for both hierarchical and flat designs.

Hierarchical split symbol support

Hierarchical split symbols can now be managed with Allegro Library Manager.

Support for managing the “standard” library

Allegro EDM 17.2 now supports the standard library that contains the page borders, ioports, taps, power symbols, etc., so that librarians can not only manage these parts, engineers can stay connected to the database to select them.